Electronics | Free Full-Text | An Optimal Digital Filtering Technique for Incremental Delta-Sigma ADCs Using Passive Integrators

Decimation Lowpass Filters for SIGMA-DELTA Modulators - A Comparative Study: Kusch, Rüdiger: 9783640862658: Amazon.com: Books

![Sigma Delta A/D Converter SamplerModulator Decimation Filter x(t) x[n]y[n] Analog Digital fsfs fsfs 2 f o 16 bits e[n] Over Sampling Ratio = 2f o is Nyquist. - ppt download Sigma Delta A/D Converter SamplerModulator Decimation Filter x(t) x[n]y[n] Analog Digital fsfs fsfs 2 f o 16 bits e[n] Over Sampling Ratio = 2f o is Nyquist. - ppt download](https://slideplayer.com/5873238/19/images/slide_1.jpg)

Sigma Delta A/D Converter SamplerModulator Decimation Filter x(t) x[n]y[n] Analog Digital fsfs fsfs 2 f o 16 bits e[n] Over Sampling Ratio = 2f o is Nyquist. - ppt download

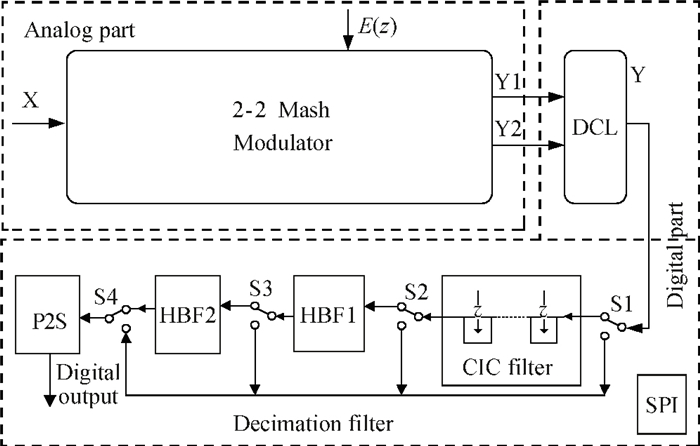

![PDF] Design and Implementation of Decimation Filter for 13-bit Sigma-Delta ADC Based on FPGA | Semantic Scholar PDF] Design and Implementation of Decimation Filter for 13-bit Sigma-Delta ADC Based on FPGA | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/4ed83bea560a9cea1094c5de9706800e53f1af00/6-Figure11-1.png)

PDF] Design and Implementation of Decimation Filter for 13-bit Sigma-Delta ADC Based on FPGA | Semantic Scholar