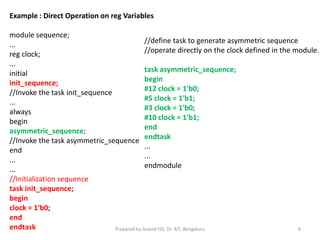

2. Functions and Tasks (call by reference) , automatic keyword, timescale in SystemVerilog - YouTube

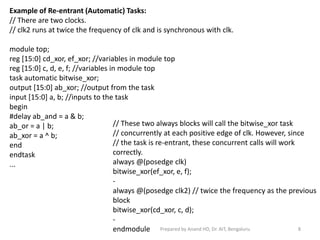

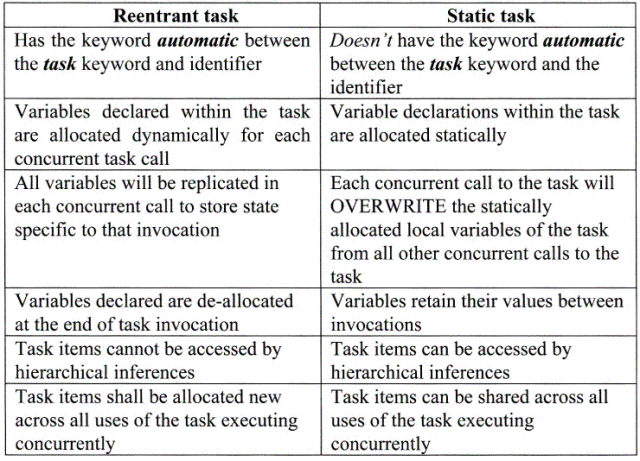

Verilog: FAQ Are tasks and functions re-entrant, and how are they different from static task and function calls? | SoC Design and Verification

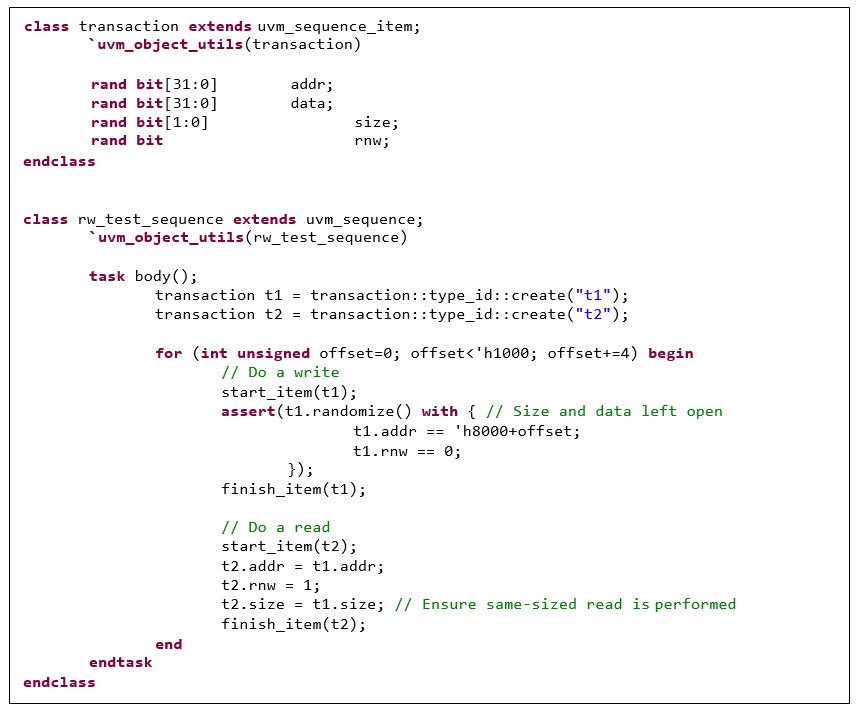

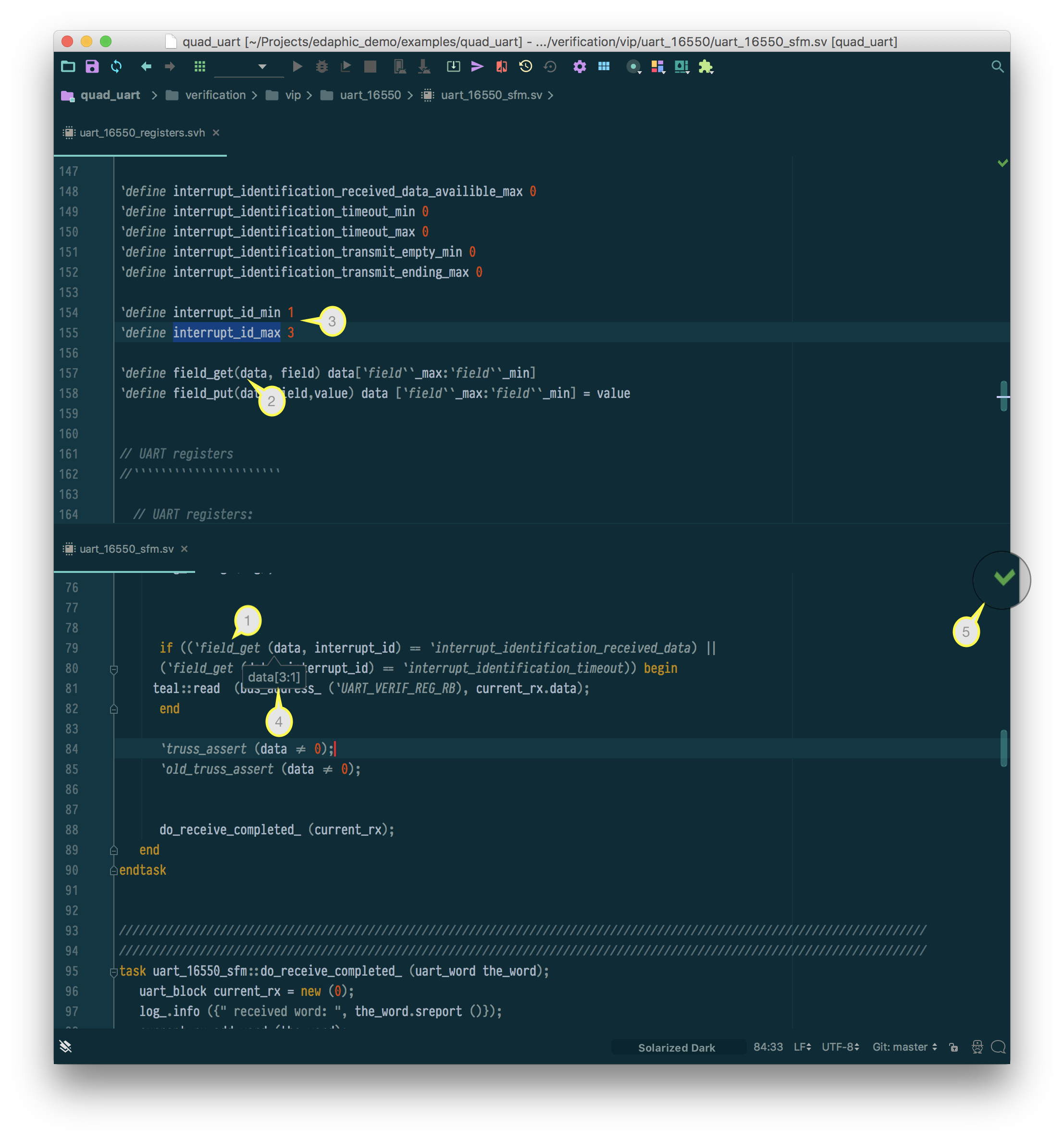

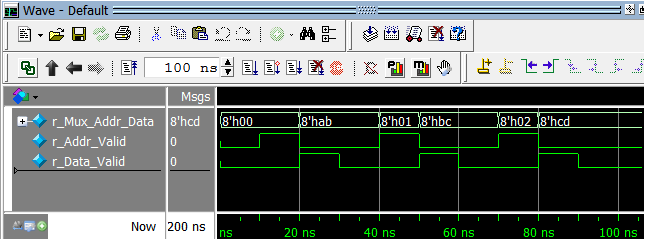

A SystemVerilog DPI Framework for Reusable Transaction Level Testing, Debug and Analysis of SoC Designs

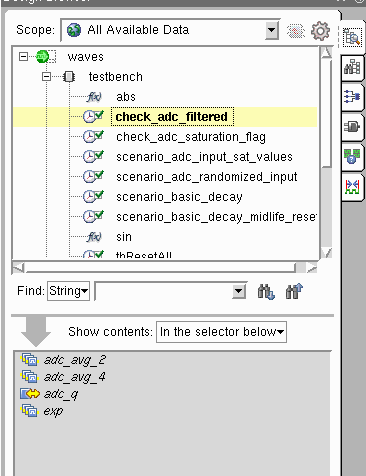

probe tcl syntax to save variables inside automatic tasks in systemverilog - Functional Verification - Cadence Technology Forums - Cadence Community

![systemverilog] automatic keyword systemverilog] automatic keyword](https://img1.daumcdn.net/thumb/C176x176/?fname=https://blog.kakaocdn.net/dn/bRNoGW/btqUseEzxkZ/xdPJZuqDZXXGasvE2upl3k/img.png)